Theo một thông tin rò rỉ mới về kiến trúc AMD Zen 7 sắp ra mắt, AMD được cho là đang có kế hoạch giới thiệu một “lõi 3D” mới cho cấu trúc CPU của mình. Dường như không chỉ nói về một nhóm bộ nhớ đệm bổ sung khổng lồ ở đây, như đã thấy trên các chip gần đây như AMD Ryzen 7 9800X3D, mà là một lớp nhiều lát bộ nhớ đệm nằm ngay bên dưới một số lượng lớn lõi CPU, trong một cấu trúc có thể trở thành một phần tiêu chuẩn của kiến trúc công nghệ trong tương lai.

Vì vẫn chưa thấy CPU AMD Zen 6, chứ đừng nói đến Zen 7, nên sẽ còn rất lâu nữa chúng ta mới thấy công nghệ này được sử dụng trong các thiết kế CPU chơi game tốt nhất. Leaker cho biết Zen 7 dự kiến sẽ ra mắt vào cuối năm 2027 hoặc đầu năm 2028, tức là còn ít nhất hai năm rưỡi nữa, nhưng nhiều người đang thực sự tò mò về cách công nghệ AMD mới này có thể hoạt động.

Những thông tin chi tiết được đồn đoán về AMD Zen 7 này được chia sẻ bởi người tiết lộ công nghệ Moore’s Law is Dead (MLID) trên YouTube, tuy vậy đây chỉ là thông tin tham khảo. Đặc biệt là vì đây thực sự là những ngày đầu để thảo luận về Zen 7, tuy nhiên, AMD đã có một số thành công lớn với chip X3D tận dụng công nghệ xếp chồng silicon 3D của TSMC và việc công ty này phát triển thêm công nghệ này là điều hợp lý.

Vậy thì Lõi 3D này là gì? “Tôi cho rằng ý tôi là V-cache, đúng không? Chỉ là lõi X3D thôi”, MLID nói. “Thực ra, câu trả lời là không. Câu trả lời ở đây là có một loại Lõi 3D hoàn toàn mới sử dụng thiết kế xếp chồng 3D để có nhiều bộ nhớ đệm và nhiều hiệu suất hơn với số lượng lõi tăng lên”.

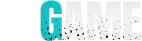

Theo thông tin rò rỉ, chiplet lõi AMD Zen 7 sẽ được sản xuất bằng công nghệ 1,4nm của TSMC, đây thực sự là công nghệ tiên tiến trong khung thời gian này nếu điều này là sự thật. Tuy nhiên, AMD được cho là sẽ tiếp tục sử dụng quy trình 4nm của TSMC để sản xuất bộ nhớ đệm V 3D. MLID cũng chia sẻ những gì ông tuyên bố là một phần của sơ đồ hiển thị cấu trúc của một phần kiến trúc Zen 7, mà bạn có thể thấy bên dưới.

Trong đó, bạn có thể thấy một lớp chứa nhiều bộ phận được dán nhãn “Lõi PT” – MLID tuyên bố rằng một chiplet Zen 7 duy nhất có thể chứa 33 lõi PT này. Theo nhiều cách thì đây là một con số kỳ lạ, và YouTuber này thừa nhận điều đó nhưng vẫn giữ nguyên quan điểm.

Theo MLID, ý tưởng đằng sau thiết kế bị rò rỉ này là việc xếp chồng 3D các lát đệm L3 theo cách này sẽ làm giảm độ trễ, mặc dù nó cũng sẽ làm giảm đáng kể không gian chiếm dụng của một chiplet và bộ đệm của nó trên gói, đồng thời cũng có khả năng đảm bảo rằng mỗi lõi có thể truy cập trực tiếp vào một lượng bộ đệm khổng lồ.